Secuencia de arranque

Los procesadores RISC-V, al contrario que los ARM, no poseen, en su configuración base, un vector de interrupciones, es una extensión estándar pero no forma parte del núcleo en sí. Por tanto, el concepto que existe en los ARM de una tabla de interrupciones en la que el "reset" es una interrupción más, no existe en RISC-V: En los RISC-V existe el "RESET_VECTOR", que es la dirección de memoria desde donde arranca el procesador cuando se reinicia o se enciende. Dicha dirección suele ser 0x00000000 pero puede ser libremente definida por el fabricante, en el caso que nos ocupa, el GD32VF103 incluye un bootloader en la dirección 0x00000000, mientras que en la dirección 0x08000000 se encuentra la memoria flash de programa (los 128 Kb). Cuando el micro arranca en modo bootloader (determinado por un pin), arranca desde la dirección 0x00000000 (RESET_VECTOR = 0x00000000), ejecuta el bootloader y éste se encarga de poner el micro en modo DFU a través del USB, mientras que cuando arranca en modo normal (sin bootloader), el micro arranca desde la dirección 0x08000000 (RESET_VECTOR = 0x08000000), donde se supone que debe estar el programa principal.

Algo parecido ocurre con el puntero de pila: Al contrario que los Cortex-M de ARM, en los RISC-V no existe una tabla que indique el valor que debe tener, en el momento del arranque, el registro de pila (SP), por lo que dicho registro debe ser cargado a mano mediante una instrucción en ensamblador. Por ejemplo, una secuencia de arranque mínima podría ser:

reset_vector:

la sp, 0x20005000 ; la SRAM acaba en 0x20005000 y la pila "crece" hacia abajo

call main ; llamamos a la función main

Nótese que no se está teniendo el cuenta la inicialización de variables globales (incluidos los constructores de objetos globales), pero es un punto de partida.

Linker script y arranque

Basándonos en un post anterior hacemos un linker script básico y un código de arranque e inicialización para variables globales y constructores. En este caso, al principio del linker script dividimos el código generado en dos zonas:

- Una al principio, en 0x08000000, donde sólo alojaremos una instrucción de salto.

- Otra a partir de 0x08000200 donde alojaremos la inicialización y el resto del código (incluida la función main).

Esto lo hacemos así porque en el caso del GD32VF103 sí que existe, para la extensión de las interrupciones de RISC-V, una tabla de interrupciones que se extiende desde 0x0800000C hasta 0x080001FC, por lo que, para poder en un futuro usar ese vector de interrupciones, haremos que el grueso del código de aloje a partir de 0x08000200 y en 0x08000000 lo que ponemos es un salto incondicional a 0x08000200.

SECTIONS {

. = 0x08000000 ;

.text : {

startup.o (.startup0)

}

. = 0x08000200 ;

.text : {

_linker_code = . ;

startup.o (.startup1)

*(.text)

*(.text.*)

*(.rodata*)

*(.gnu.linkonce.t*)

*(.gnu.linkonce.r*)

}

.preinit_array : {

__preinit_array_start = . ;

*(.preinit_array)

__preinit_array_end = . ;

}

.init_array : {

__init_array_start = . ;

*(.init_array)

__init_array_end = . ;

}

.fini_array : {

__fini_array_start = . ;

*(.fini_array)

__fini_array_end = . ;

}

.ctors : {

__CTOR_LIST__ = . ;

LONG((__CTOR_END__ - __CTOR_LIST__) / 4 - 2)

*(.ctors)

LONG(0)

__CTOR_END__ = . ;

}

.dtors : {

__DTOR_LIST__ = . ;

LONG((__DTOR_END__ - __DTOR_LIST__) / 4 - 2)

*(.dtors)

LONG(0)

__DTOR_END__ = . ;

}

...Como se puede ver, se definen dos secciones al principio del linker script:

- Una a partir de la dirección 0x08000000 y en la que se alojará el código de las funciones etiquetadas con la sección ".startup0" del fichero startup.o.

- Otra a partir de la dirección 0x08000200 y en la que se alojará primero el código de las funciones que se encuentren etiquetadas con la sección ".startup1" seguido por el resto del código del programa.

A continuación se ubican las secciones estándar ".preinit_array", ".init_array", ".ctors" encargadas de alojar las llamadas a los constructores y las funciones de inicialización de variables globales, y las secciones estándar ".fini_array" y ".dtors", encargadas de alojar las llamadas a los destructores y las funciones de destrucción de variables globales (esta parte del código no se debería ejecutar jamás en un sistema embebido, se incluye por elegancia).

Variables globales en RAM y copia de datos de Flash a RAM

...

flash_sdata = . ;

. = 0x20000000 ;

ram_sdata = . ;

.data : AT (flash_sdata) {

_linker_data = . ;

*(.data)

*(.data.*)

*(.gnu.linkonce.d*)

}

ram_edata = . ;

data_size = ram_edata - ram_sdata;

ram_sbssdata = . ;

.bss : AT (LOADADDR(.data) + SIZEOF(.data)) {

_linker_bss = . ;

*(.bss)

*(.bss.*)

*(.gnu.linkonce.b.*)

*(.COMMON)

}

ram_ebssdata = . ;

bssdata_size = ram_ebssdata - ram_sbssdata;

_linker_end = . ;

end = . ;

}

En esta parte del linker script se indica que la dirección virtual de los datos es 0x20000000 (esta es la dirección que se usará desde el código de programa para acceder a los datos en RAM), pero sin embargo dichos datos están inicialmente alojados en la memoria flash (a continuación de la sección ".dtors"), por lo que es necesario un copiado de dichas variables globales inicializadas desde la memoria flash hasta la RAM antes de que se ejecute la función "main".

Código de arranque

En el fichero startup.cc se definen dos funciones _startup_0 y _startup_1 y se etiquetan como de las secciones ".startup0" y ".startup1", respectivamente. La función _startup_0 está definida con el atributo "naked" (para que el compilador no genere código de preámbulo ni postámbulo) y contiene una única instrucción de salto:

void _startup_0() __attribute__((section(".startup0"), naked)); void _startup_0() { asm volatile ( "j %0" : : "i" (_startup_1) ); }

Esta es la función que se aloja en la dirección 0x08000000 y que, como se vio antes, es la encargada de saltar a _startup_1. La función _startup_1, que también está definida como "naked" pero etiquetada en la sección ".startup1" (por lo que se aloja a partir de la dirección 0x08000200) alberga el resto de código de inicialización:

void _startup_1() __attribute__((section(".startup1"), naked)); void _startup_1() { asm volatile ( "la sp, 0x20005000" // point SP to the end of SRAM ); _initClock(); _initDataRAM(); _initBssRAM(); _callConstructors(); _callInitArray(); main(); _callFiniArray(); _callDestructors(); while (true) ; }

Y realiza lo siguiente:

1. Inicializa el puntero de pila para que apunte al final de la RAM (el puntero de pila se decrementa cuando se hace "push" y se incrementa cuando se hace "pop").

2. Inicializa los PLLs del microcontrolador para configurar el reloj de cristal (en mi caso he dejado esta función vacía por lo que el microcontrolador queda funcionando con el reloj RC interno que es más lento pero suficiente para nuestro blinker).

3. Inicializa la RAM que se copia desde la flash (ver aquí los detalles de este proceso).

4. Inicializa la RAM que debe estar a cero (BSS).

5. Invoca las funciones de inicialización y los constructores.

6. Finalmente incova a la función "main".

Al final se coloca una especie de código "de cortesía" para que, en el caso de que la función "main" regrese (cosa que no debería ocurrir), se invoquen los destructores y el micro se quede "colgado" (bucle infinito).

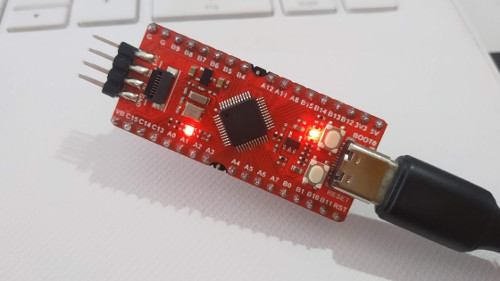

Prueba de concepto

Se ha optado por hacer un simple blinker basado en esperas estándar de ciclos de procesador, en lugar de un timer, ya que, como se comentó antes, el núcleo básico de un RISC-V no incluye interrupciones y creo que es mejor abordarlas en una siguiente entrega:

#includeusing namespace std; #define RCU_APB2EN *((uint32_t *) 0x40021018) #define GPIOC_CTL1 *((uint32_t *) 0x40011004) #define GPIOC_OCTL *((uint32_t *) 0x4001100C) int main() { // enable clock on port C RCU_APB2EN |= ((uint32_t) 1) << 4; // PC13 pin is output, low speed, push-pull GPIOC_CTL1 = 0x44244444; while (true) { for (uint32_t i = 0; i < 200000; i++) ; GPIOC_OCTL ^= (((uint32_t) 1) << 13); } }

La placa en la que está alojada el GD32VF103 es una Longan Nano que posee un led tricolor con la componente roja conectada al pin PC13 del micro. Para hacer parpadear este led rojo debemos:

1. Habilitar el reloj interno de la circuitería GPIO del micro.

2. Configurar el pin PC13 como GPIO de salida en push-pull.

3. Modificar el bit 13 del registro asociado de forma periódica para hacer que el led parpadee.

Los registros son una copia casi exacta de los del STM32F103 por lo que si estás acostumbrado a ese micro de ST, adaptarte al GD32VF103 será muy sencillo.

Bootloader

Cuando arranca el microcontrolador GD32VF103, si el pin BOOT0 se encuentra a nivel 1, no se arranca desde la dirección 0x08000000, sino que se ejecuta un "bootloader" interno que configura el microcontrolador como un dispositivo USB con interfaz estándar DFU (Device Firmware Upgrade). Se trata de un estándar conocido y para el que existen herramientas como dfu-util (que, en el caso de Linux, sólo requiere de la librería "libusb"). Con el microcontrolador en modo DFU y el comando "dfu-util" podemos "tostar" nuestro ejecutable "main.bin" de forma muy sencilla:

dfu-util --dfuse-address 0x08000000 -D main.bin

En la sección soft está todo el código disponible.

[ añadir comentario ] ( 1777 visualizaciones ) | [ 0 trackbacks ] | enlace permanente |

( 3 / 2184 )

( 3 / 2184 )Los procesadores RISC-V empiezan a hacerse poco a poco un huequito en nuestros corazones. A continuación pongo las instrucciones para compilar la toolchain cruzada de GNU (GCC) para RISC-V con newlib.

Se trata de una toolchain para sistemas "bare metal", sin sistema operativo, por lo que no tiene soporte para multihilos ni para librerías dinámicas.

binutils 2.36

mkdir -p /opt/baremetalriscv/src

mkdir -p /opt/baremetalriscv/build

cd /opt/baremetalriscv/src

wget https://ftp.gnu.org/gnu/binutils/binutils-2.36.tar.bz2

tar xf binutils-2.36.tar.bz2

cd ../build

mkdir binutils-2.36

cd binutils-2.36/

../../src/binutils-2.36/configure --prefix=/opt/baremetalriscv --target=riscv32-none-elf --disable-nls

make

make install

gcc 11.1.0 (stage 1)

cd /opt/baremetalriscv/src

wget https://ftp.gnu.org/gnu/gcc/gcc-11.1.0/gcc-11.1.0.tar.gz

wget https://ftp.gnu.org/gnu/gmp/gmp-6.2.1.tar.bz2

wget https://ftp.gnu.org/gnu/mpc/mpc-1.2.1.tar.gz

wget https://ftp.gnu.org/gnu/mpfr/mpfr-4.1.0.tar.gz

tar xf gcc-11.1.0.tar.gz

tar xf gmp-6.2.1.tar.bz2

tar xf mpc-1.2.1.tar.gz

tar xf mpfr-4.1.0.tar.gz

mv gmp-6.2.1 gcc-11.1.0/gmp

mv mpc-1.2.1 gcc-11.1.0/mpc

mv mpfr-4.1.0 gcc-11.1.0/mpfr

cd ../build/

mkdir gcc-11.1.0-stage-1

cd gcc-11.1.0-stage-1/

export PATH=/opt/baremetalriscv/bin:${PATH}

../../src/gcc-11.1.0/configure --prefix=/opt/baremetalriscv --target=riscv32-none-elf --enable-languages=c --without-headers --disable-nls --disable-threads --disable-shared --disable-libssp --with-newlib

make all-gcc all-target-libgcc

make install-gcc install-target-libgcc

newlib

cd /opt/baremetalriscv/src

git clone git://github.com/riscv/riscv-newlib.git

cd ../build

mkdir newlib

cd newlib

../../src/riscv-newlib/configure --prefix=/opt/baremetalriscv --target=riscv32-none-elf

make

make install

gcc 11.1.0 (stage 2)

cd /opt/baremetalriscv/build

mkdir gcc-11.1.0-stage-2

cd gcc-11.1.0-stage-2/

../../src/gcc-11.1.0/configure --prefix=/opt/baremetalriscv --target=riscv32-none-elf --enable-languages=c,c++ --disable-nls --disable-threads --disable-shared --disable-libssp --with-newlib --with-headers=../../src/riscv-newlib/newlib/libc/include

make

make install

El compilador de C++ de GCC 11.1 compila por defecto en modo C++17 y soporta prácticamente todo el estándar C++20.

ACTUALIZACIÓN: El proceso de compilación descrito sirve también para gcc-12.2, binutils-2.40 y el repositorio de newlib oficial (git://sourceware.org/git/newlib-cygwin.git) puesto que el proyecto riscv-newlib ya se ha integrado en el proyecto oficial de newlib.

[ añadir comentario ] ( 1312 visualizaciones ) | [ 0 trackbacks ] | enlace permanente |

( 3 / 2116 )

( 3 / 2116 )La literatura existente relacionada con el diseño de filtros digitales suele incidir en el estudio de determinados filtros ya conocidos, como paso-bajo, paso-alto, paso-banda, etc., a veces calculados a partir de la discretización de filtros analógicos y sin entrar en detalles de diseño o sin abordar el problema de forma directa (sin discretizar). A lo largo de este artículo se abordará el diseño directo de un filtro resonante sencillo.

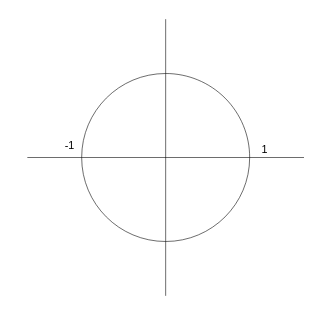

Plano z

La herramienta fundamental para el cálculo de filtros digitales es la transformada Z y su plano complejo asociado, denominado "plano z". Se asume que el lector está medianamente familiarizado con la transformada z y no se abordarán los detalles ni las propiedades de la misma.

La transformada z transforma una función, situada en el dominio discreto del tiempo $x[n]$, en otra función, situada en el dominio complejo de z $X(z)$. Esta transformación es equivalente a la transformada de Laplace en el dominio continuo y tiene ambas propiedades similares en cuanto a linealidad y estabilidad. Al igual que la transformada de Laplace, la transformada Z también se utiliza para modelar funciones de transferencia de sistemas, en el caso de la transformada Z, son sistemas discretos.

Es decir, si para un filtro analógico tenemos una función de transferencia $H(s)$, caracterizada principalmente por sus ceros y sus polos, para un filtro digital tendremos también una función de transferencia $H(z)$, caracterizada también por sus ceros y sus polos. Tanto en el caso de Laplace como en el caso Z los ceros determinan para qué tipo de señales el filtro "tiende a cancelar la entrada" y los polos determinan para qué tipo de señales el filtro "tiende a amplificar la entrada" o incluso entrar en resonancia. La regla básica que debe cumplirse en un filtro analógico es que los polos de $H(s)$ nunca deben tener parte real positiva (deben estar siempre localizados en el semiplano izquierdo del plano complejo $s$), mientras que en caso de un filtro digital, los polos de $H(z)$ nunca deben alojarse fuera de la circunferencia unitaria centrada en el origen del plano complejo $z$ (es decir, los polos en un filtro digital deben cumplir que $|z| < 1$).

Diseño de un filtro resonante sencillo

En el plano z no se mapean frecuencias absolutas como en el plano s, sino que se mapean frecuencias "relativas" a la frecuencia de muestreo y a lo largo de la longitud de la circunferencia de radio 1. La frecuencia asociada a un valor complejo del plano z se corresponde con el ángulo (argumento) de dicho valor: un ángulo de 0 radianes se corresponde con un valor en continua (0 Hz) mientras que un valor de $\pi$ radianes se corresponde con la mitad de la frecuencia de muestreo (frecuencia Nyquist). Si, por ejemplo, muestreamos a 44100 Hz, la frecuencia máxima ($\pi$) será de 22050 Hz, mientras que si muestreamos a 8000 Hz la misma frecuencia PI se corresponderá con 4000 Hz.

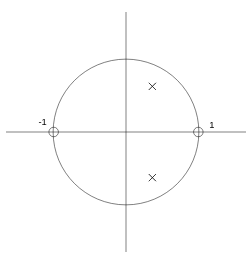

El diseño básico de filtros digitales es muy sencillo y se resume en cuatro reglas principales:

- Alojar tantos ceros sobre la circunferencia de radio 1 como frecuencias queramos cancelar. Lo importante de cada cero será su ángulo (= frecuencia) con respecto al origen. Por ejemplo si colocamos un cero en en punto $z = 1$, que se corresponde con un ángulo de 0 radianes, nuestro filtro eliminará la componente de continua de la señal.

- Alojar tantos polos DENTRO de la circunferencia de radio 1 ($|z| < 1$) como frecuencias queramos amplificar. En este caso es importante tanto el ángulo (= frecuencia que queremos reforzar) como su magnitud o módulo (= nivel de refuerzo). Si hacemos que la magnitud (el módulo) de un polo sea 1 ($|z| = 1$) el filtro auto-oscilará a esa frecuencia. Por ejemplo, si colocamos un polo en $z = -1$, que se corresponde con un ángulo $\pi$, estaremos reforzando las señales con frecuencia próxima a $\pi$ (= la mitad de la frecuencia de muestreo).

- Los polos y ceros que tengan parte imaginaria diferente de 0 deberán ponerse por pares conjugados para poder trabajar con señales reales (sin componente imaginaria). Por ejemplo, si estamos muestreando a 44100 Hz y queremos cancelar las frecuencias próximas a 11025 Hz (frecuencia ${\pi \over 2}$), debemos colocar DOS polos conjugados: uno en $(0, 1)$, formando un ángulo de 90 grados (${\pi \over 2}$) y otro en $(0, -1)$ (su conjugado).

- Al final lo habitual es también ajustar la ganancia global del filtro (aunque en este caso no lo hemos hecho por simplicidad). Esto se hace habitualmente debido a que a veces los polos meten mucha ganancia en la banda de paso y es necesario escalar la salida antes de emitirla o la entrada antes de procesarla.

Si, por ejemplo, queremos hacer un filtro paso bajo, lo habitual, es poner un cero en $z = -1$ (sobre la circunferencia de radio 1 con ángulo $\pi$) con el objetivo de anular las altas frecuencias y un polo (con su complejo conjugado) cerca de la frecuencia de corte de nuestro filtro. En nuestro caso de estudio, se trata de un filtro resonante sencillo, por lo que definiremos dos ceros: uno en $z = 1$ (0 radianes), y otro en $z = -1$, ($\pi$ radianes). Como queremos una única frecuencia de resonancia, definimos un único polo (junto con su complejo conjugado, por lo que realmente serán dos polos).

Con esta configuración de dos ceros reales en -1 y 1 y dos polos complejos conjugados en la frecuencia de resonancia tenemos la siguiente función de transferencia en Z:

$$H(z) = {(z + 1)(z - 1) \over (z - p_1)(z - p_1^\prime)}$$

Para la que se cumple que:

$$p_1 = a + bi \;\;\;\;\;\;\;\;\; p_1^\prime = a - bi$$

Desarrollando el denominador (los polos) de $H(z)$ tenemos que:

$$(z - p_1)(z - p_1^\prime) = z(z - p_1^\prime) - p_1(z - p_1^\prime)$$

$$ = z^2 - zp_1^\prime -p_1z + p_1p_1^\prime$$

$$ = z^2 - z(p_1^\prime + p_1) + p_1p_1^\prime$$

$$ = z^2 - z2a + p_1p_1^\prime$$

$$ = z^2 - z2a + a^2 + b^2$$

Nótese que, al ser los polos complejos conjugados, las operaciones

$(p_1^\prime + p_1)$ y $p_1p_1^\prime$ dan como resultado, valores reales (sin componente imaginaria). Por otro lado, si desarrollamos el numerador (los ceros) de $H(z)$ tenemos que:

$$(z + 1)(z - 1) = z(z - 1) + (z - 1)$$

$$ = z^2 - z + z - 1$$

$$ = z^2 - 1$$

Por tanto la función de transferencia $H(z)$ puede reescribirse de la siguiente manera:

$$H(z) = {{z^2 - 1} \over {z^2 - z2a + a^2 + b^2}}$$

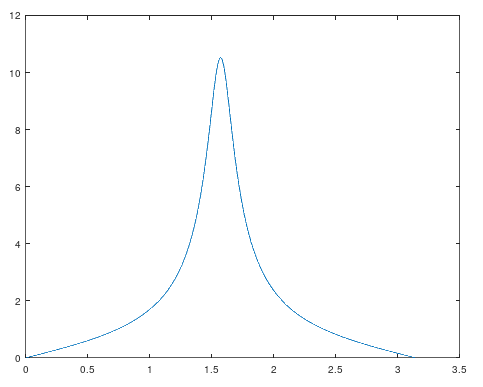

Podemos visualizar la respuesta en frecuencia de este sistema asignando a z diferentes valores sobre la circunferencia unitaria $z = e^{iw} = cos(w) + i sen(w)$:

Para generar esta gráfica se ejecutó el siguiente código octave que sitúa el polo (= la frecuencia de resonancia del filtro) en ${\pi \over 2}$:

m = 0.9; w = pi / 2; a = m * cos(w); b = m * sin(w); # respuesta en frecuencia TAM = 1000; responseX = zeros(1, TAM); responseY = zeros(1, TAM); for n = 1:TAM w = (n / TAM) * pi; responseX(n) = w; z = cos(w) + (i * sin(w)); responseY(n) = abs(((z * z) - 1) / ((z * z) - (z * 2 * a) + (a * a) + (b * b))); endfor plot(responseX, responseY);

Implementación del filtro

Ahora que ya tenemos la función de transferencia en el dominio Z del filtro que queremos, el siguiente paso es pasar al dominio discreto y calcular los coeficientes en diferencias finitas para poder implementarlo. Lo primero que se hace es evitar que haya exponentes mayores que 0 para z (exponentes positivos de z se corresponden a muestras "futuras" en el tiempo). Esto se soluciona de forma muy sencilla multiplicando numerador y denominador de $H(z)$ por $z^{-2}$, esto mantiene $H(z)$ igual pero elimina los exponentes positivos:

$$H(z) = {{z^2 - 1} \over {z^2 - z2a + a^2 + b^2}}$$

$$H(z) = {{z^{-2}(z^2 - 1)} \over {z^{-2}(z^2 - z2a + a^2 + b^2)}}$$

$$H(z) = {{1 - z^{-2}} \over {1 - z^{-1}2a + z^{-2}(a^2 + b^2)}}$$

Ahora ya podemos calcular los coeficientes de forma más sencilla. Como $H(z)$ es una función de transferencia en Z tenemos que, si $X(z)$ es la transformada Z de la entrada e $Y(z)$ es la transformada Z de la salida, entonces:

$$Y(z) = H(z) X(z) = {{1 - z^{-2}} \over {1 - z^{-1}2a + z^{-2}(a^2 + b^2)}} X(z)$$

Y, por tanto:

$$Y(z)(1 - z^{-1}2a + z^{-2}(a^2 + b^2)) = X(z)(1 - z^{-2})$$

$$Y(z)-Y(z)z^{-1}2a+Y(z)z^{-2}(a^2 + b^2) = X(z) - X(z)z^{-2}$$

Como la transformada Z es lineal y se cumple que la transformada Z de un valor desplazado k muestras en el tiempo es la siguiente:

$$Z \left\{ x[n - k] \right\} = X(z)z^{-k}$$

Entonces podemos hacer la antitransformada Z de forma sencilla:

$$y[n] - y[n - 1]2a + y[n - 2](a^2 + b^2) = x[n] - x[n - 2]$$

Y, despejando $y[n]$ tenemos que:

$$y[n] = x[n] - x[n - 2] + y[n - 1]2a - y[n - 2](a^2 + b^2)$$

Esto, como se puede ver, es una ecuación en diferencias finitas, que es muy fácil de implementar tanto en hardware como en software. Veamos una ejemplo de código octave que genera ruido blanco y luego lo hace pasar por el filtro (aplica la ecuación en diferencias finitas con los mismos valores a y b, esto es, misma frecuencia de resonancia en ${\pi \over 2}$).

m = 0.9; w = pi / 2; a = m * cos(w); b = m * sin(w); TAM = 1000; input = (rand(1, N) .* 2) .- 1; # TAM valores aleatorios entre -1 y 1 ym1 = 0; ym2 = 0; xm1 = 0; xm2 = 0; output = zeros(1, TAM); for n = 1:TAM output(n) = input(n) - xm2 + (ym1 * 2 * a) - (ym2 * ((a * a) + (b * b))); ym2 = ym1; ym1 = output(n); xm2 = xm1; xm1 = input(n); endfor subplot(2, 2, 1) plot(input); title('Ruido'); subplot(2, 2, 2) plot(output); title('Ruido filtrado'); subplot(2, 2, 3) plot(abs(fft(input)(1:(N / 2)))); title('Espectro del ruido'); subplot(2, 2, 4) plot(abs(fft(output)(1:(N / 2)))); title('Espectro del ruido filtrado');

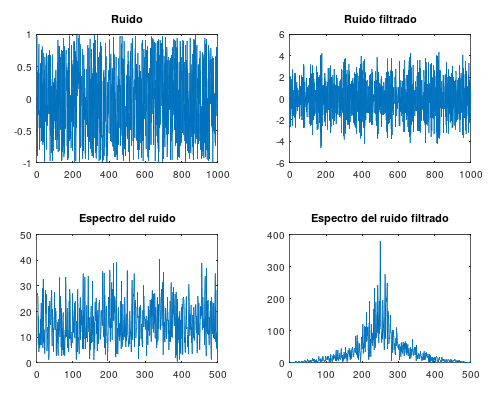

A continuación se pueden ver las señales y los espectros en frecuencia de las mismas y se puede comprobar como el funcionamiento del filtro es el esperado:

[ añadir comentario ] ( 2336 visualizaciones ) | [ 0 trackbacks ] | enlace permanente |

( 3 / 2138 )

( 3 / 2138 )El proyecto navideño de este año es una sencilla estrella de navidad que puede colocarse tanto en el árbol como en el belén y que requiere de muy poca circuitería.

Idea

El objetivo era no recurrir a la típica luz parpadeante sino darle un efecto de movimiento, que parezca que la estrella se mueva por el firmamento. Para simular este efecto lo más sencillo es alinear varias luces y hacer que la luz se mueva rápidamente, con un brillo creciente y en una dirección concreta, lo que da el efecto de que la luz un efecto meteorito.

Diseño eléctrico

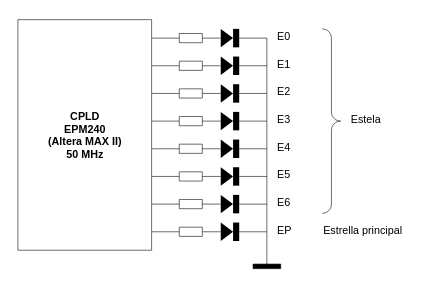

A nivel electrónico el concepto es muy sencillo: 8 leds de alta luminosidad protegidos con resistencias y conectados a 8 salidas de un CPLD.

Uno de los leds hace de estrella principal mientras que los 7 leds restantes servirán para hacer el efecto de la estela de la estrella principal. La secuencia de iluminación será la siguiente:

- E0 iluminado al 5%, resto apagado

- E1 iluminado al 10%, resto apagado

- E2 iluminado al 15%, resto apagado

- E3 iluminado al 20%, resto apagado

- E4 iluminado al 30%, resto apagado

- E5 iluminado al 40%, resto apagado

- E6 iluminado al 50%, resto apagado

- EP iluminado al 100% durante varias unidades de tiempo más, resto apagado

- Todo apagado durante varias unidades de tiempo

Diseño lógico y funcionamiento

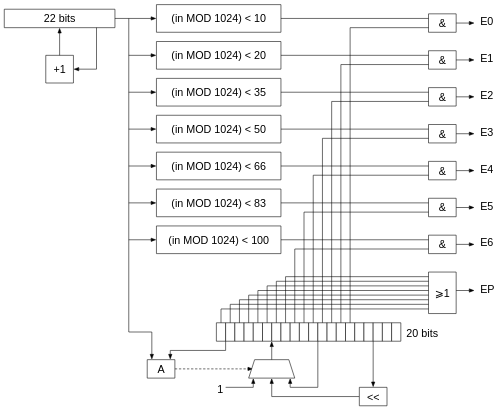

A continuación una propuesta de diagrama de bloques sencillo:

Al circuito combinacional A tiene como entradas el valor del registro contador de 22 bits y el valor del registro de desplazamiento de 20 bits y como salida la entrada de selección del multiplexor del registro de desplazamiento de 20 bits:

| registro contador | reg. desplaz. | mux |

|---|---|---|

| x | 0 | valor 1 |

| 0 | x | salida desplazador izquierda |

| ≠0 | ≠0 | reg. desplaz. (mantener) |

El registro contador se utiliza con dos propósitos:

- Como medida de unidad de tiempo: Cada vez que se desborda, se desplaza el registro de desplazamiento. A 50 MHz de frecuencia de reloj, tenemos una frecuencia de desplazamiento de ${50000000 \over {2^{22}}} = 11.92093 \: Hz$, es decir ${1 \over 11.92093} = 0.08389 \: seg$, aproximadamente una décima de segundo como unidad de tiempo.

- Como registro contador para el PWM de los leds de la estela: Como es un contador estándar de desbordamiento, se pueden usar los 10 bits menos significativos para generar una señal PWM, esto nos da una frecuencia de señal PWM de ${50000000 \over {2^{10}}} \approx 49 \: KHz$ que es una buena frecuencia para un led.

Al iniciarse el CPLD todos los bits del registro de desplazamiento estarán a 0, lo que provocará que el circuito combinacional A emita un 1 para que, en el primer ciclo de reloj, se cargue un 1 en el registro de desplazamiento. A partir de aquí el circuito combinacional A mantendrá el multiplexor en modo "copia" (manteniendo el valor del registro de desplazamiento) y sólo mandará a desplazar cuando el registro contador se desborde. El registro de desplazamiento tendrá un bit 1 moviéndose de izquierda a derecha a razón de un salto cada décima de segundo, cuando el bit llega al extremo izquierdo aparece de nuevo en el extremo derecho del registro (formalmente deberíamos llamar al registro de desplazamiento, registro de "rotación").

Los 5 bits menos significativos del registro de desplazamiento no se conectan a nada, lo que significa que durante unas 5 décimas de segundo (medio segundo aproximadamente) ninguna de las luces se enciende, cuando el 1 pasa al bit 5 del registro de desplazamiento, se pone a 1 la entrada inferior de la puerta AND que gobierna el led E0, que hace las veces de enable para la salida PWM con menor ciclo de trabajo (menor luminosidad). Cuando el 1 pasa al bit 6 del registro de desplazamiento, se pone a 1 la entrada inferior de la puerta AND que gobierna el led E1, que hace de enable para la salida PWM con ciclo de trabajo ligeramente superior (un poco más de limunosidad que el anterior) y así sucesivamente. A medida que el 1 va desplazándose a la izquierda (un salto por cada décima de segundo aproximadamente) se van iluminando los leds E0 a E6 de forma consecutiva y con ciclos de trabajo PWM crecientes (es decir, cantidad de luz creciente). Los últimos 8 bits del registro de desplazamiento (bits 19 al 12) están conectados a una puerta OR que gobierna la luz EP (estrella principal), esto hace que la estrella principal esté encendida unas 8 décimas de segundo, y luego vuelta a empezar.

Implementación

A continuación el código VHDL:

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity MaxIIBethlehemStar is port ( ClkIn : in std_logic; BoardLedOut : out std_logic; StarOut : out std_logic; Wake1Out : out std_logic; Wake2Out : out std_logic; Wake3Out : out std_logic; Wake4Out : out std_logic; Wake5Out : out std_logic; Wake6Out : out std_logic; Wake7Out : out std_logic ); end entity; architecture A of MaxIIBethlehemStar is constant Intensity1PWM : integer := 100; -- over 1024 constant Intensity2PWM : integer := 83; constant Intensity3PWM : integer := 66; constant Intensity4PWM : integer := 50; constant Intensity5PWM : integer := 35; constant Intensity6PWM : integer := 20; constant Intensity7PWM : integer := 10; signal TimerDBus : std_logic_vector(21 downto 0); signal TimerQBus : std_logic_vector(21 downto 0); signal ShiftDBus : std_logic_vector(19 downto 0); signal ShiftQBus : std_logic_vector(19 downto 0); signal Intensity1 : std_logic; signal Intensity2 : std_logic; signal Intensity3 : std_logic; signal Intensity4 : std_logic; signal Intensity5 : std_logic; signal Intensity6 : std_logic; signal Intensity7 : std_logic; begin -- intensity signals (using timer lower 10 bits as PWM counter) Intensity1 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity1PWM, 10)) else '1'; Intensity2 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity2PWM, 10)) else '1'; Intensity3 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity3PWM, 10)) else '1'; Intensity4 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity4PWM, 10)) else '1'; Intensity5 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity5PWM, 10)) else '1'; Intensity6 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity6PWM, 10)) else '1'; Intensity7 <= '0' when (unsigned(TimerQBus(9 downto 0)) > to_unsigned(Intensity7PWM, 10)) else '1'; -- timer counter process (ClkIn) begin if (ClkIn'event and (ClkIn = '1')) then TimerQBus <= TimerDBus; end if; end process; TimerDBus <= std_logic_vector(unsigned(TimerQBus) + to_unsigned(1, 22)); -- shift register process (ClkIn) begin if (ClkIn'event and (ClkIn = '1')) then ShiftQBus <= ShiftDBus; end if; end process; ShiftDBus <= std_logic_vector(to_unsigned(1, 20)) when (unsigned(ShiftQBus) = 0) else ShiftQBus(18 downto 0) & ShiftQBus(19) when (unsigned(TimerQBus) = 0) else ShiftQBus; -- outputs StarOut <= ShiftQBus(19) or ShiftQBus(18) or ShiftQBus(17) or ShiftQBus(16) or ShiftQBus(15) or ShiftQBus(14) or ShiftQBus(13) or ShiftQBus(12); Wake1Out <= Intensity1 and ShiftQBus(11); Wake2Out <= Intensity2 and ShiftQBus(10); Wake3Out <= Intensity3 and ShiftQBus(9); Wake4Out <= Intensity4 and ShiftQBus(8); Wake5Out <= Intensity5 and ShiftQBus(7); Wake6Out <= Intensity6 and ShiftQBus(6); Wake7Out <= Intensity7 and ShiftQBus(5); -- debug BoardLedOut <= (ShiftQBus(19) or ShiftQBus(18) or ShiftQBus(17) or ShiftQBus(16) or ShiftQBus(15) or ShiftQBus(14) or ShiftQBus(13) or ShiftQBus(12)) or (Intensity1 and ShiftQBus(11)) or (Intensity2 and ShiftQBus(10)) or (Intensity3 and ShiftQBus(9)) or (Intensity4 and ShiftQBus(8)) or (Intensity5 and ShiftQBus(7)) or (Intensity6 and ShiftQBus(6)) or (Intensity7 and ShiftQBus(5)); end architecture;

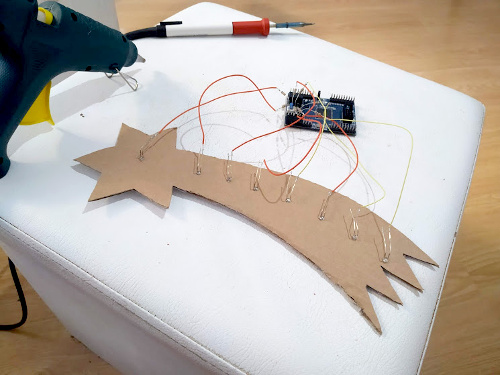

El montaje se ha implementado sobre un CPLD MAX II de Altera, usando leds blancos de alta luminosidad y montándolos luego sobre una base de cartón duro con la típica forma de estrella de navidad.

El código fuente está disponible en la sección soft. ¡Feliz Navidad y feliz 2021!

[ añadir comentario ] ( 1601 visualizaciones ) | [ 0 trackbacks ] | enlace permanente |

( 3 / 2124 )

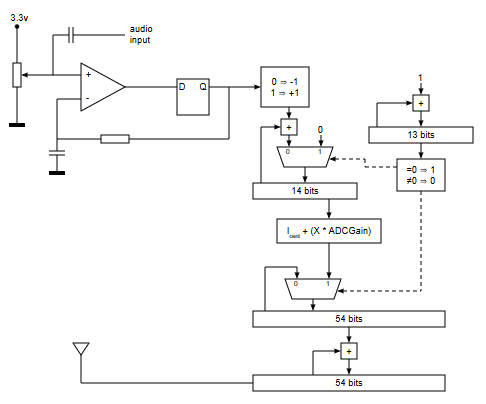

( 3 / 2124 )En anteriores entradas se realizó la implementación, tanto de un transmisor FM como de un conversor analógico digital delta-sigma, sobre FPGA y como proyectos separados. A lo largo de esta entrada se aborda el desarrollo de un transmisor FM en la banda de la radio comercial para transmitir música, combinando ambos proyectos en uno solo.

Conversión analógica digital delta-sigma

Como se puede comprobar en el post anterior relacionado, la conversión analógica digital de tipo delta-sigma tiene la ventaja de requerir muy pocos componentes externos: un comparador analógico (para lo que puede usarse un amplificador operacional normal), un condensador y una resistencia; y permite implementar un ADC de precisión arbitraria (la precisión sólo está limitada por los recursos disponibles en la FPGA).

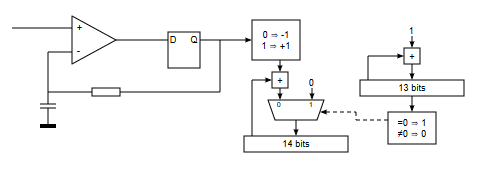

Recordemos que la conversión analógico digital de tipo delta-sigma lo que hace es, mediante un biestable de tipo D, hacer que la salida que carga el condensador C a través de la resistencia R "siga" a la entrada analógica:

- Si la entrada + del comparador está por encima de la entrada -, el comparador emite un 1, que es cargado en el siguiente ciclo de reloj por el biestable de entrada, haciendo que la salida que va a la resistencia R tome el valor de 1 y trate de "acercar" el valor de la entrada - del comparador al valor de la entrada + del comparador.

- Si la entrada + del comparador está por debajo de la entrada -, el comparador emite un 0, que es cargado en el siguiente ciclo de reloj por el biestable de entrada, haciendo que la salida que va a la resistencia R tome el valor de 0 y trate de "acercar" (esta vez hacia "abajo") el valor de la entrada - del comparador al valor de la entrada + del comparador.

Como se puede ver, este comportamiento hace que para valores próximos a 0 voltios en la entrada + del comparador, el biestable de entrada emite muchos más 0s que 1s, mientras que para valores próximos a 3.3 voltios en la entrada + del comparador, el biestable de entrada emite muchos más 1s que 0s. También se puede ver que para valores próximos a Vcc / 2 = 1.65 voltios, el biestable emitirá una cantidad aproximadamente igual de 0s que de 1s.

Si lo que hacemos ahora es asociar al valor 0 de la salida del biestable, el valor numérico -1, y, al valor 1 de la salida del biestable, el valor numérico +1, lo que tenemos es un circuito digital que emitirá:

- Más +1 que -1 para valores próximos a 3.3 voltios.

- Más -1 que +1 para valores próximos a 0 voltios.

- Una cantidad aproximadamente igual de -1 y +1 para valores próximos a 1.65 voltios.

Si vamos acumulando estos -1 y +1 sobre un acumulador que se pone a cero cada cierto tiempo, lo que tendremos es que en dicho acumulador tendremos un valor proporcional al voltaje de entrada del ADC:

- Valores próximos a 3.3 voltios, al generar más +1 que -1, dan como resultado un valor de conversión muy alto y positivo.

- Valores próximos a 0 voltios, al generar más -1 que +1, dan como resultado un valor de conversión muy bajo y negativo.

- Valores próximos a 1.65 voltios, al generar una cantidad aproximadamente similar de -1 y de +1, dan como resultado un valor de conversión próximo a 0.

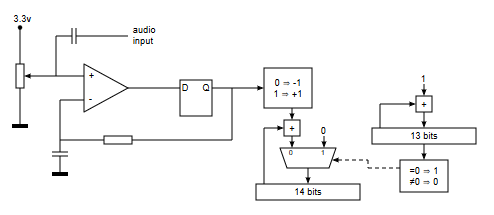

Debido a esta necesidad de contar -1s y +1s necesitamos sobremuestreo: Si queremos obtener una resolución de 16 bits, eso significa que el valor máximo de conversión tendrá que ser -32767 mientras que el valor mínimo de conversión tendrá que ser -32768. Si asumimos una escala simétrica tendremos un valor entre -32767 y +32767, eso significa que debemos hacer 32767 sumas (de -1s y +1s) antes de leer el valor de conversión. Dichas sumas las tenemos que hacer en un registro, que llamaremos "acumulador de conversión".

Para el caso de 16 bits necesitaríamos un contador de 15 bits que, en el momento de que valga 0 haga que el "acumulador de conversión" copie su valor en el registro de salida del ADC y se ponga a cero, y, durante los 32767 pulsos restantes (hasta el siguiente desbordamiento), se sumen los -1s y +1s que van entrando.

Así vemos que, por ejemplo, para 12 MHz y 16 bits de resolución, como necesitaríamos un contador de 15 bits, al final la frecuencia de muestreo podrá ser, como máximo de:

$$ {12000000 \over {2^{15}}} = 366.21 \: Hz $$

Por ejemplo, si queremos hacer una conversión en calidad CD necesitaríamos un reloj de sistema (sobremuestreo) de:

$$ {44100 \times {2^{15}}} = 1445068800 \: Hz $$

En el caso que nos ocupa se ha decidido implementar el transmisor en una FPGA MAX10 de las que viene en una placa MAX1000 de Arrow, a 12 MHz, cuyo reloj puede ser subido mediante PLLs hasta unos 400 MHz. Debido a esta limitación se ha decidido subir el reloj a 300 MHz y, para trabajar con esa frecuencia de sobremuestreo, se han tenido que bajar un poco las especificaciones del ADC, usando un contador de 13 bits y un acumulador de conversión de 14 bits. De esta forma tenemos una frecuencia de muestreo de:

$$ {300000000 \over {2^{13}}} = 36621.09375 \: Hz $$

Por lo que el ancho de banda es de unos 18 KHz (buen ancho de banda para música) y la resolución de conversión es de 14 bits (valores de conversión entre -8191 y +8191). No es calidad CD pero tampoco está mal.

Consideraciones entorno a la entrada de sonido analógica

Hay que tener en cuenta que las señales de sonido tal cual salen de un amplificador, son señales simétricas (con semiciclos positivos y negativos) mientras que nuestro ADC mide voltajes entre 0 y 3.3 voltios (no mide voltajes negativos). Es necesario, por tanto, acondicional la señal de sonido de entrada para que quede "desplazada" hacia arriba y un valor de 0 voltios de entrada se traduzca en 1.65 voltios a la entrada + del comparador. Es por esto por lo que se coloca el divisor de tensión entre 3.3 y 0 voltios a la entrada de audio, que desplaza el "0" de la señal de sonido hasta los 1.65 voltios.

El nivel de señal que entrega la salida de auriculares de un ordenador es suficiente para la entrada del ADC y no requiere amplificación adicional, al menos para esta prueba.

Generador de señal de antena

La frecuencia de transmisión elegida es 87.5 MHz (el extremo inferior de la banda de radiodifusión de sonido). La señal de antena que se quiere generar debe estar centrada, por tanto, en dicha frecuencia y dicha frecuencia deberá variarse en un rango máximo de +-75 KHz (estándar de radiodifusión). Para la generación de frecuencias arbitrarias que sean inferiores a la frecuencia de reloj de un sistema digital lo lógico es utilizar un acumulador de fase.

Un acumulador de fase no es más que un registro que se incrementa en un valor constante (no tiene por qué incrementarse de 1 en 1) con desbordamiento. Por ejemplo, si a partir de un reloj de 300 MHz queremos generar un reloj de 75 MHz lo que podemos hacer es incrementar un registro de 2 bits de 1 en 1 a 300 MHz:

...

Pulso: 00 --> 01

Pulso: 01 --> 10

Pulso: 10 --> 11

Pulso: 11 --> 00

Pulso: 00 --> 01

Pulso: 01 --> 10

Pulso: 10 --> 11

Pulso: 11 --> 00

...

En este ejemplo se puede ver que si la frecuencia de pulso es de 300 MHz, la frecuencia del bit 0 será de ${300 \over 2} = 150 \: MHz$ mientras que la frecuencia del bit 1 será de ${150 \over 2} = 75 \: MHz$. Un acumulador de fase con incrementos potencia de 2 es, formalmente, un divisor de frecuencia. Si se aplica este mismo principio para registros con mayor cantidad de bits y usando incrementos arbitrarios, conseguimos frecuencias diferentes.

Asumamos que la señal de salida de nuestro "oscilador" será siempre el bit más significativo de un registro de 16 bits y nuestro reloj va a 300 MHz. Eso significará que, incrementando el registro de 1 en 1, el bit más significativo cambiará a razón de:

$$ {300000000 \over {2^N}} = 4577 \: Hz $$

Si en lugar de incrementar el registro de 1 en 1, lo incrementamos de 2 en 2, la cantidad de pulsos que tarde en desbordarse el registro será menor, por tanto, la frecuencia del bit más significativo será mayor, es decir, la frecuencia del bit más significativo es proporcional al valor de incremento del registro. El máximo valor de incremento será $2^{N-1}$ para N bits (es decir un 1 seguido de N-1 ceros) que hará que el registro se comporte de la siguiente manera:

...

Pulso: 0000000000000000 --> 1000000000000000

Pulso: 1000000000000000 --> 0000000000000000

Pulso: 0000000000000000 --> 1000000000000000

Pulso: 1000000000000000 --> 0000000000000000

...

En este caso extremo tenemos que la frecuencia del bit más significativo es de 150 MHz (para una frecuencia de pulso de 300 MHz). De forma genérica tenemos que el valor de incremento para una frecuencia dada puede calcularse de la siguiente forma:

$$ I = {{f_{deseada}} \over 300000000} \times 2^{N} $$

En nuestro caso, si queremos emitir a 87.5 MHz hay que usar un valor de N=54 bits para que el valor de incremento no sea fraccionario:

$$ I_{central} = {87500000 \over 300000000} \times 2^{54} = 5254199565265579 $$

Ese valor es el que habría que usar como valor de incremento en cada pulso de reloj para que en el bit más significativo del registro de 54 bits (bit 53) tengamos una señal a 87.5 MHz. Nótese que para valores de incremento que no sean potencias de 2, obtendremos señales no cuadradas o de fase algo irregular (en el anterior post dedicado a la transmisión FM se profundiza en este tema), pero para el caso que nos ocupa, la "calidad" de la señal resultante no es significativa, lo importante es que la frecuencia fundamental sea la correcta. Para hacer modulación en frecuencia hemos de modificar esta frecuencia en el rango de -75 KHz y +75 KHz, lo que nos genera los siguiente incrementos mínimos y máximos:

$$ I_{min} = {(87500000 - 75000) \over 300000000} \times 2^{54} = 5249695965638208 $$

$$ I_{max} = {(87500000 + 75000) \over 300000000} \times 2^{54} = 5258703164892949 $$

Si calculamos la diferencia entre los incrementos y la dividimos entre dos nos dará el valor 4503599627370.5 que es la amplitud máxima que deberá tener la señal del ADC para que modifique el valor del incremento y que este, a su vez, genere una variación máxima de +- 75 KHz en la frecuencia portadora.

Como la salida del ADC da valores entre -8191 y +8191 a este valor hay que multiplicarle el valor ${4503599627370.5 \over 8191} = 549822930$ para que valores próximos a -8191 en la salida del ADC generen una portadora de 87.5 MHz - 75 KHz = 87.425 MHz y valores próximos a +8191 en la salida del ADC generen una portadora de 87.5 MHz + 75 KHz = 87.575 MHz. El valor del incremento del acumulador de fase que genera la señal de la antena será el siguiente:

$$ I = I_{central} + (ADC \times 549822930) = 5254199565265579 + (ADC \times 549822930) $$

A continuación puede verse el código fuente completo (cabe en un único fichero VHDL).

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity MAX10FMTransmitter is port ( Clk : in std_logic; AnalogComparator : in std_logic; PWM : out std_logic; Antenna : out std_logic; Led : out std_logic_vector(7 downto 0) ); end entity; architecture A of MAX10FMTransmitter is component PLL port ( inclk0 : in std_logic := '0'; c0 : out std_logic ); end component; signal Clk300 : std_logic; signal ADCFollowerD : std_logic; signal ADCFollowerQ : std_logic; signal ADCScalerD : std_logic_vector(12 downto 0); signal ADCScalerQ : std_logic_vector(12 downto 0); signal ADCAccumulatorD : std_logic_vector(13 downto 0); signal ADCAccumulatorQ : std_logic_vector(13 downto 0); -- signed value: -8191 to +8191 signal ADCOutputD : std_logic_vector(13 downto 0); signal ADCOutputQ : std_logic_vector(13 downto 0); signal PhaseAccumulatorD : std_logic_vector(53 downto 0); signal PhaseAccumulatorQ : std_logic_vector(53 downto 0); signal PhaseAccumulatorIncD : std_logic_vector(53 downto 0); signal PhaseAccumulatorIncQ : std_logic_vector(53 downto 0); -- increment for phase accumulator to transmit at 87.5 MHz: (87500000 / 300000000) * (2^54) = 5254199565265579 --constant TxCentralFrequencyInc : integer := 5254199565265579; -- must fit in 54 bits constant TxCentralFrequencyIncL : integer := 2863311531; -- 32 bits constant TxCentralFrequencyIncH : integer := 1223338; -- 22 bits constant TXCentralFrequencyInc : signed(53 downto 0) := to_signed(TxCentralFrequencyIncH, 22) & to_signed(TxCentralFrequencyIncL, 32); -- gain for ADC output constant ADCGain : integer := 549822930; -- ADCGain needs 30 bits begin -- PLL to obtain 300 MHz from external 12 MHz P : PLL port map ( inclk0 => Clk, c0 => Clk300 ); -- ADC process (Clk300) begin if (Clk300'event and (Clk300 = '1')) then ADCFollowerQ <= ADCFollowerD; end if; end process; ADCFollowerD <= AnalogComparator; PWM <= ADCFollowerQ; process (Clk300) begin if (Clk300'event and (Clk300 = '1')) then ADCScalerQ <= ADCScalerD; end if; end process; ADCScalerD <= std_logic_vector(unsigned(ADCScalerQ) + 1); process (Clk300) begin if (Clk300'event and (Clk300 = '1')) then ADCAccumulatorQ <= ADCAccumulatorD; end if; end process; ADCAccumulatorD <= std_logic_vector(to_signed(0, 14)) when (unsigned(ADCScalerQ) = 0) else std_logic_vector(signed(ADCAccumulatorQ) + to_signed(1, 14)) when (ADCFollowerQ = '1') else std_logic_vector(signed(ADCAccumulatorQ) - to_signed(1, 14)) when (ADCFollowerQ = '0') else ADCAccumulatorQ; process (Clk300) begin if (Clk300'event and (Clk300 = '1')) then ADCOutputQ <= ADCOutputD; end if; end process; ADCOutputD <= ADCAccumulatorQ when (unsigned(ADCScalerQ) = 0) else ADCOutputQ; Led <= ADCOutputQ(13 downto 6); -- phase accumulator process (Clk300) begin if (Clk300'event and (Clk300 = '1')) then PhaseAccumulatorQ <= PhaseAccumulatorD; end if; end process; PhaseAccumulatorD <= std_logic_vector(unsigned(PhaseAccumulatorQ) + unsigned(PhaseAccumulatorIncQ)); Antenna <= PhaseAccumulatorQ(53); -- phase accumulator increment control (output frequency control) process (Clk300) begin if (Clk300'event and (Clk300 = '1')) then PhaseAccumulatorIncQ <= PhaseAccumulatorIncD; end if; end process; -- 14 bits * 40 bits = 54 bits PhaseAccumulatorIncD <= std_logic_vector((signed(ADCAccumulatorQ) * to_signed(ADCGain, 40)) + TxCentralFrequencyInc) when (unsigned(ADCScalerQ) = 0) else PhaseAccumulatorIncQ; end architecture;

El bit 53 del registro acumulador de fase se saca por un pin de la FPGA y en dicho pin se puede colocar un simple trozo de cable. No es necesario hacer ningún circuito que acondicione la señal de salida.

Si a corta distancia del circuito ponemos un receptor de radio FM comercial sintonizado a 87.5 MHz podremos escuchar la señal que está leyendo el ADC de la FPGA y que está siendo transmitida en FM.

Código fuente disponible en la sección soft.

[ añadir comentario ] ( 1754 visualizaciones ) | [ 0 trackbacks ] | enlace permanente |

( 3 / 2182 )

( 3 / 2182 )

Calendario

Calendario