Motivación

En la anterior entrada del blog se realizó un pequeño proyecto para generar dos efectos de sonido utilizando un sencillo chip PSG, el SN76489. Los sonidos generados fueron muy buenos pero a nivel hardware, como el objetivo del montaje es una futura integración en un pequeño robot con mando a distancia, me encontré con que, el hecho de tener que cablear todo un bus de 8 bits junto con los pines OE y READY, consumía muchos pines del STM32 (el robot consume ya GPIO y PWM para las ruedas, UART para la comunicación e I2C para una pequeña pantalla OLED).

Una primera aproximación válida sería un conversor serie a paralelo de tipo I2C o algo así pero instalar DOS chips sólo para generar dos ruidos rudimentarios me pareció excesivo, por lo que opté por una solución basada en un CPLD.

64 macroceldas

Ese es el reto: hacer un generador de sonido que consuma, como mucho, 64 macroceldas en un CPLD de la serie MAX3000A de Intel, en concreto el EPM3064.

64 macroceldas son 64 biestables con la lógica combinatoria asociada. No es un reto sencillo y es probable que los resultados no tengan tan buena calidad como con un PSG, pero el beneficio que se consigue en reducción de pines, miniaturización y reducción de consumo (Un CPLD consume mucho para los estándares actuales, pero el SN76489 consume más) hace que valga la pena intentarlo.

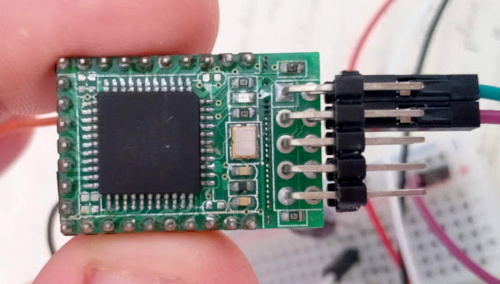

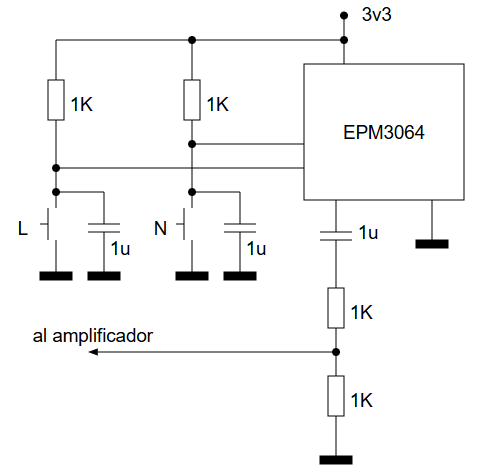

El circuito

Se plantea un circuito sencillo con dos entradas configuradas en lógica negativa y circuitería antirrebote básica y una salida con condensador de desacoplo y divisor de tensión para evitar sobretensiones en el amplificador de audio de la salida. La placa equipada con el CPLD EPM3064 incluye un oscilador a 50 MHz conectado a uno de los pines de reloj del CPLD y un led con su cátodo conectado a otro de los pines del CPLD (se enciende cuando se emite un 0 por ese pin).

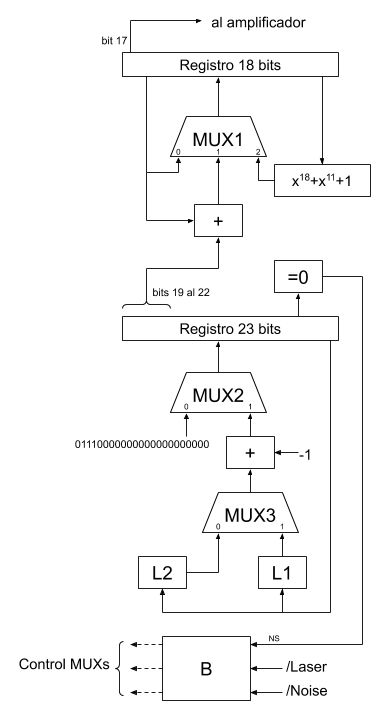

Diagrama de bloques

A continuación puede verse el diagrama del bloques que se ha implementado en el CPLD.

El bloque $x^{18} + x^{11} + 1$ se corresponde con el LFSR maximal de grado 18 que permite generar ruido blanco (aproximado) en el registro de arriba.

L1 es un bloque combinacional que emite un 1 si la entrada vale 0 y la entrada sin cambiar en caso contrario.

| L1 | |

|---|---|

| Entrada | Salida |

| 0 | 1 |

| x | x |

L2 es un bloque combinacional que emite 8193 si la entrada vale 0 y la entrada sin cambiar en caso contrario.

| L2 | |

|---|---|

| Entrada | Salida |

| 0 | 8193 |

| x | x |

B es el bloque combinacional encargado de controlar los multiplexores en función de las señales de entrada y del cruce por cero del registro de 23 bits:

| B | |||||

|---|---|---|---|---|---|

| Entradas | Salidas (MUX) | ||||

| /Laser | /Noise | NS | 1 | 2 | 3 |

| 1 | 1 | dc | 1 | 1 | 1 |

| 0 | dc | dc | 0 | 0 | dc |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 2 | 1 | 0 |

Descripción funcional

Cuando se activa la entrada /Laser (se pone a nivel bajo), se carga en el registro de 23 bits el valor "01110000000000000000000", este valor se carga para que los 4 bits más significativos tengan el valor "0111". Si nos fijamos los 4 bits más significativos del registro de 23 bits se utlizan para incrementar el valor del registro de 18 bits. Dicho registro de 18 bits actúa como acumulador de fase para una señal de onda cuadrada correspondiente al bit más significativo (bit 17) de este registro.

Si tenemos un registro de 18 bits como acumulador de fase y una frecuencia de reloj de 50 MHz (la de la placa que estamos usando) tendremos una frecuencia del bit más significativo de:

$$f_{out} = {f_{clk} \over 2^{18}}$$

De forma general, en caso de que apliquemos incrementos arbitrarios a este registro de desplazamiento, obtendremos una frecuencia en el bit más significativo de:

$$f_{out} = Inc \times {f_{clk} \over 2^{18}} = Inc \times {50000000 \over 2^{18}}$$

Para simular el sonido de un disparo láser lo que generamos es una caida rápida en frecuencia por lo que empezamos con un $Inc = 7$ cuando /Laser = 0 (de ahí los 4 bits más significativos del valor 01110000000000000000000), este valor de incremento genera una frecuencia en el bit más significativo del registro de 18 bits de:

$$Inc = 7 \Rightarrow f_{out} = 7 \times {50000000 \over 2^{18}} = 1335.1 Hz$$

Cuando /Laser vuelve al valor 1, vamos bajando el valor de Inc (los 4 bits más significativos del registro de 23 bits) hasta que vale 0:

$$Inc = 6 \Rightarrow f_{out} = 1144.4 Hz$$

$$Inc = 5 \Rightarrow f_{out} = 953.67 Hz$$

$$Inc = 4 \Rightarrow f_{out} = 762.94 Hz$$

$$Inc = 3 \Rightarrow f_{out} = 572.2 Hz$$

$$Inc = 2 \Rightarrow f_{out} = 381.47 Hz$$

$$Inc = 1 \Rightarrow f_{out} = 190.73 Hz$$

$$Inc = 0 \Rightarrow f_{out} = 0 Hz$$

Como el registro de 23 bits también actúa como un acumulador de fase (pues se decrementa en bloque, no solo los bits más significativos), la caida es lo suficientemente lenta como para ser audible (que es lo que queremos). Nótese que una vez cae a 0, el registro de 23 bits se queda ahí estancado gracias al circuito combinacional L1 que actúa como limitador, lo que, en la práctica, provoca que el registro de 18 bits "pare" de oscilar (pues $Inc = 0$ siempre). Nótese también que, aunque pare de oscilar, es posible que a la salida que va hacia el amplificador (el bit 17) se quede un "1" de forma pemanente, es por ello por lo que se hace necesario colocar siempre un condensador de desacoplo a la salida.

Si lo que se pone a 0 es la entrada /Noise y la entrada /Laser permanece a 1, lo que se hace es seleccionar como realimentación del registro de 18 bits la salida del polinomio LFSR, que provocará una secuencia de números pseudoaleatorios (ruido) en el bit 17 (salida del amplificador). La carga del valor del LFSR no se produce en cada ciclo del reloj de 50 MHz, pues provocaría ruido no audible, sino que se aprovecha el registro de desplazamiento de 23 bits y, a través del circuito combinacional L2, se hace que "desborde" en 8192, por lo que el registro de 18 bits cambiará con una frecuencia de:

$$f_{muestreo} = {50000000 \over 8192} = 6103.5 Hz$$

por lo que el ruido resultante ocupará aproximadamente hasta la banda de los 3 KHz. No es un ruido blanco pero a efectos audibles es muy parecido al ruido generado por un PSG.

Código fuente

Todo el código fuente en VHDL puede meterse dentro de una sola entidad:

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity Epm3064GunSound is port ( Clk : in std_logic; TrigLaserIn : in std_logic; TrigNoiseIn : in std_logic; SpeakerOut : out std_logic; LedOut : out std_logic ); end entity; architecture Architecture1 of Epm3064GunSound is signal LFSRD : std_logic_vector(17 downto 0); signal LFSRQ : std_logic_vector(17 downto 0); signal LFSRRawOut : std_logic_vector(17 downto 0); signal LFSROut : std_logic_vector(17 downto 0); signal LFSRMux : std_logic_vector(1 downto 0); signal TimerD : std_logic_vector(22 downto 0); signal TimerQ : std_logic_vector(22 downto 0); signal TimerMux : std_logic; signal Limited1TimerQ : std_logic_vector(22 downto 0); signal Limited2TimerQ : std_logic_vector(22 downto 0); signal LimiterMux : std_logic; signal LimiterMuxOut : std_logic_vector(22 downto 0); signal NoiseSample : std_logic; begin -- LFSR process (Clk) begin if (Clk'event and (Clk = '1')) then LFSRQ <= LFSRD; end if; end process; --LFSRRawOut <= (LFSRQ(0) xor LFSRQ(3)) & LFSRQ(19 downto 1); 20 bits LFSRRawOut <= (LFSRQ(0) xor LFSRQ(7)) & LFSRQ(17 downto 1); -- 18 bits LFSROut <= LFSRRawOut when (unsigned(LFSRRawOut) /= 0) else std_logic_vector(to_unsigned(1, 18)); LFSRD <= LFSROut when (LFSRMux = "10") else std_logic_vector(unsigned(LFSRQ) + unsigned(TimerQ(22 downto 19))) when (LFSRMux = "01") else LFSRQ; SpeakerOut <= LFSRQ(17); -- timer process (Clk) begin if (Clk'event and (Clk = '1')) then TimerQ <= TimerD; end if; end process; Limited1TimerQ <= std_logic_vector(to_unsigned(1, 23)) when (signed(TimerQ) = 0) else TimerQ; Limited2TimerQ <= std_logic_vector(to_unsigned(8192 + 1, 23)) when (signed(TimerQ) = 0) else TimerQ; LimiterMuxOut <= Limited1TimerQ when (LimiterMux = '1') else Limited2TimerQ; TimerD <= std_logic_vector(signed(LimiterMuxOut) - 1) when (TimerMux = '1') else "01110000000000000000000"; NoiseSample <= '1' when (signed(TimerQ) = 0) else '0'; -- operation logic LFSRMux <= "01" when (((TrigLaserIn = '1') and (TrigNoiseIn = '1')) or (TrigLaserIn = '0')) else "10" when ((TrigLaserIn = '1') and (TrigNoiseIn = '0') and (NoiseSample = '1')) else "00"; TimerMux <= '0' when (TrigLaserIn = '0') else '1'; LimiterMux <= '1' when ((TrigLaserIn = '1') and (TrigNoiseIn = '1')) else '0'; LedOut <= TrigLaserIn and TrigNoiseIn; end architecture;

Resultados

Con este circuito se consiguen unos resultados similares a los obtenidos utilizando el chip SN76489, con menos circuitería, ocupando menos pines y menos tiempo de procesamiento en el microcontrolador: nótense que ahora sólo necesitamos dos pines GPIO del microcontrolador (uno para /Laser y otro para /Noise).

Todo el código fuente puede descargarse de la sección soft.

[ añadir comentario ] ( 2492 visualizaciones ) | [ 0 trackbacks ] | enlace permanente |

( 3 / 3312 )

( 3 / 3312 )

Calendario

Calendario