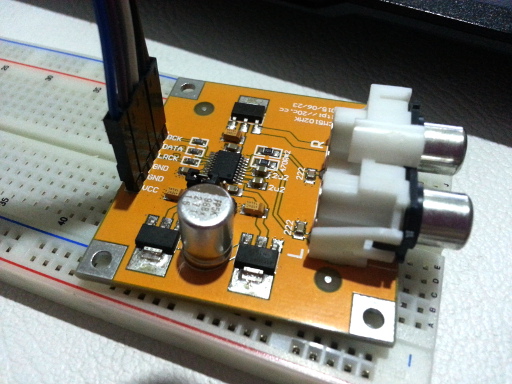

El DAC de Texas Instruments PCM5102 es un DAC que soporta el estándar I2S de transferencia de audio digital y el estándar left justified (variante del I2S). Existen muchos otros DACs de audio en el mercado con soporte para estos formatos, sin embargo los más usados son el ES9023 y derivados, de ESS, y el PCM5102 y derivados, de Texas Instruments. En mi caso, adquirí una placa con un integrado PCM5102A y la circuitería mínima (componentes pasivos, espadines para conectar alimentación y las tres líneas del protocolo I2S y dos conectores RCA hembra de salida, uno para cada canal).

Unos 14 por AliExpress (gastos de envío incluidos), aunque ahora creo que está incluso más barato.

I2S

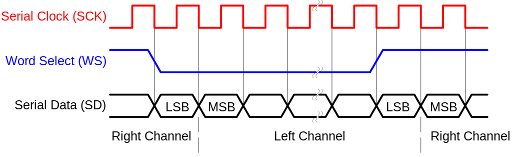

El protocolo I2S es un protocolo muy sencillo de transferencia de audio digital. Aunque por su nombre puede parecer que es un protocolo derivado o parecido al protocolo I2C, lo cierto es que sólo se parecen en el nombre y, para nuestro alivio, es bastante más sencillo que el I2C.

(imagen extraida de Wikimedia, realizada por el usuario Wdwd y con licencia Creative Commons Attribution 3.0 Unported)

El protocolo, como se puede ver en el diagrama, solo necesita de tres hilos: uno para datos, otro para el reloj y otro para seleccionar la palabra o el frame (ponemos esta señal a 0 para enviar la muestra del canal izquierdo y a 1 para enviar la muestra del canal derecho).

Al tratarse de un protocolo de transferencia serie, si queremos emitir audio con calidad CD (16 bits a 44100 Hz estéreo) hace falta generar un reloj de:

$$44100 \times 16 \times 2 = 1411200 \thinspace Hz$$

Como se puede ver, si se quiere trabajar con frecuencias de muestreo lo suficientemente altas como para asegurar una mínima calidad de audio, es necesario hardware dedicado: generar esas señales por software es muy ineficiente. En nuestro caso el microcontrolador MK20 de Freescale (ARM Cortex-M4) que viene en la placa Teensy sí que viene equipado con un interface I2S totalmente programable.

El interface I2S en el microcontrolador MK20

El interface I2S tiene dos modos: directo y mediante DMA. En esta primera aproximación he implementado el modo directo (sin DMA). Es el modo que más CPU consume pero también es el más sencillo. Los pasos para configurar la interface de salida I2S en el MK20 son, grosso modo, los siguientes:

1. Configurar el multiplexor de pines para asignar las tres señales a pines reales.

2. Configurar el los divisores de frecuencia para obtener el bit clock de I2S a partir del reloj del sistema.

3. Configurar el tamaño de palabra (16 bits estéreo en nuestro caso).

4. Colgar de la IRQ 35 la función encargada de escribir las muestras en el registro de datos I2S.

5. Habilitar la IRQ 35 (vector de interrupción 16 + 35 = 51 del ARM Cortex-M4).

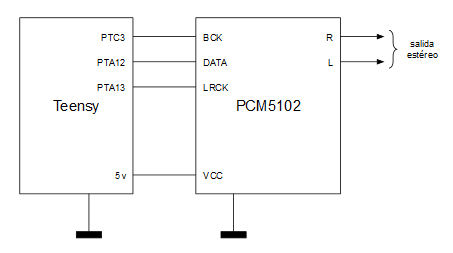

Configurar el multiplexor de pines es muy sencillo. En este caso he optado por usar la configuración ALT6 para los pines PORTA.12, PORTA.13 y PORTC.3 que les dan la funcionalidad TX, FS (frame select, el equivalente a "word select") y BCLK (bit clock) respectivamente.

Para configurar el BCLK se dispone de un divisor de frecuencia fraccionario y de un divisor de frecuencia entero. Si quisiéramos usar una frecuencia de muestreo de 48KHz haríamos los siguiente:

1. Establecemos como fuente de reloj, el reloj del núcleo (SYSCLK) que, en nuestro caso, va a 96 MHz.

2. El divisor de frecuencia fraccionario lo configuramos con el valor: 16 / 125 (96 * 16 / 125 = 12.288 MHz).

3. El divisor de frecuencia entero lo configuramos a continuación con el valor 8: 12.288 / 8 = 1.536 MHz).

En este caso: 48 KHz * 2 * 16 = 1.536 MHz.

El resto de pasos es mejor verlos en el código:

bool i2sInit() { // configure i/o pins // (PTA12 = TX, PTA13 = FS, PTC3 = BCLK) --> ALT6 PORTA_PCR12 = ((uint32_t) 6) << 8; PORTA_PCR13 = ((uint32_t) 6) << 8; PORTC_PCR3 = ((uint32_t) 6) << 8; // enable system clock for i2s module SIM_SCGC6 |= ((uint32_t) 1) << 15; // select input clock 0 and output enable I2S0_MCR = ((uint32_t) 1) << 30; #if (I2S_SAMPLE_RATE == 48000) // divide to get the 12.2880 MHz from 96MHz (96 * (16/125)) I2S0_MDR = (((uint32_t) 15) << 12) | ((uint32_t) 124); #elif (I2S_SAMPLE_RATE == 44100) // divide to get the 11.2896 MHz from 96MHz (96 * (2/17)) I2S0_MDR = (((uint32_t) 1) << 12) | ((uint32_t) 16); #elif (I2S_SAMPLE_RATE == 32050) // divide to get the 8.2051 MHz from 96MHz (96 * (10/117)) I2S0_MDR = (((uint32_t) 9) << 12) | ((uint32_t) 116); #else #error "I2S_SAMPLE_RATE must be 48000, 44100 or 32050" #endif // re-enable system clock to the i2s module SIM_SCGC6 |= ((uint32_t) 1) << 15; // disable tx (TE=0) while configuring I2S0_TCSR &= ~(((uint32_t) 1) << 31); // transmitter remains enabled until (and TE set) the end of the current frame for (int i = 0; (i < 1000) && (I2S0_TCSR & (((uint32_t) 1) << 31)); i++) ; if (I2S0_TCSR & (((uint32_t) 1) << 31)) return false; // no word mask I2S0_TMR = 0; // set FIFO watermark I2S0_TCR1 = ((uint32_t) (I2S_FRAME_SIZE - 1)); // use asynchronous mode (SYNC=0), BCLK polatiry active low (BCP=0), select master clock 1 (MSEL=1), bit clock divide (DIV=3), BCLK internally generated I2S0_TCR2 = (((uint32_t) 1) << 25) | (((uint32_t) 1) << 26) | ((uint32_t) 3) | (((uint32_t) 1) << 24); // transmit data channel is enabled (TCE=1) I2S0_TCR3 = (((uint32_t) 1) << 16); // frame size (FRSZ), bits per frame sync (SYWD), MSB (MF=1), I2S standard (not "left justified") (FSE=1), frame sync in master mode (FSD) I2S0_TCR4 = (((uint32_t) (I2S_FRAME_SIZE - 1)) << 16) | (((uint32_t) (I2S_IO_BIT_DEPTH - 1)) << 8) | (((uint32_t) 1) << 4) | (((uint32_t) 1) << 3) | ((uint32_t) 1); // bits per word for first word in each frane (W0W), bits per word for rest of words in each frame (WNW), bit index for first bit tx (MSB, 15-th for 16 bit) //I2S0_TCR5 = (((uint32_t) (I2S_IO_BIT_DEPTH - 1)) << 16) | (((uint32_t) (I2S_IO_BIT_DEPTH - 1)) << 24) | (((uint32_t) 15) << 8); I2S0_TCR5 = (((uint32_t) (I2S_IO_BIT_DEPTH - 1)) << 16) | (((uint32_t) (I2S_IO_BIT_DEPTH - 1)) << 24) | (((uint32_t) (I2S_IO_BIT_DEPTH - 1)) << 8); return true; } void i2sStart() { wavePtr = (int16_t *) &_binary_drum_loop_16_raw_start; NVIC_ENABLE_IRQ(IRQ_I2S0_TX); // tx enable (TE=1), bit clock enable (BCE=1), FIFO request interrupt enable, FIFO reset I2S0_TCSR |= (((uint32_t) 1) << 31) | (((uint32_t) 1) << 28) | (((uint32_t) 1) << 8) | (((uint32_t) 1) << 25); } void i2sStop() { NVIC_DISABLE_IRQ(IRQ_I2S0_TX); }

Además de lo dicho, es necesario colgar de la IRQ 35 una rutina que será invocada tantas veces por segundo como indique la frecuencia de muestreo y que será la encargada de escribir en el registro de salida I2S las muestras de audio que se van a emitir por la interface I2S. Definimos la rutina de la siguiente manera dentro del codigo C++:

extern char _binary_drum_loop_16_raw_start; extern char _binary_drum_loop_16_raw_end; volatile char *p; void i2sTx() __attribute__ ((section(".i2s_tx"))); volatile int16_t *wavePtr; void i2sTx() { // if FRF=0, return if (!(I2S0_TCSR & (((uint32_t) 1) << 16))) return; // write left and right sample I2S0_TDR0 = (uint32_t) *wavePtr; I2S0_TDR0 = (uint32_t) *wavePtr; wavePtr++; if (wavePtr >= ((int16_t *) &_binary_drum_loop_16_raw_end)) wavePtr = (int16_t *) &_binary_drum_loop_16_raw_start; // if underrun, clear underrun if (I2S0_TCSR & (((uint32_t) 1) << 18)) I2S0_TCSR |= (((uint32_t) 1) << 18); // if frame sync error, clear frame sync error flag if (I2S0_TCSR & (((uint32_t) 1) << 19)) I2S0_TCSR |= (((uint32_t) 1) << 19); }

Y en el linker script de nuestro proyecto incluimos una seccion especial a la que llamaremos .cortex_m4_vector_i2s_tx y que ubicamos en la direccion de memoria 0x000000CC (la correspondiente a la IRQ 35). En esta sección ponemos la dirección de memoria de nuestra rutina de servicio de interrupción (la encargada de escribir las muestras), es decir metemos la dirección de memoria I2S_TX_ADDRESS + 1 (recordar que al tratarse de un Cortex-M, el reportorio de instrucciones es siempre el reportorio thumb y, por lo tanto, los destinos de salto para subrutinas y para codigo siempre deben tener su bit 0 a 1).

SECTIONS {

. = 0x00000000 ;

.cortex_m4_vectors : {

LONG(0x20007FFC);

LONG(0x00000411);

}

. = 0x000000CC ;

.cortex_m4_vector_i2s_tx : {

LONG(I2S_TX_ADDRESS + 1);

}

. = 0x00000400 ;

.flash_configuration : {

LONG(0xFFFFFFFF);

LONG(0xFFFFFFFF);

LONG(0xFFFFFFFF);

LONG(0xFFFFFFFE);

}

.text : {

_linker_code = . ;

init.o (.text)

*(.text)

*(.text.*)

*(.rodata*)

*(.gnu.linkonce.t*)

*(.gnu.linkonce.r*)

}

I2S_TX_ADDRESS = . ;

.i2s_tx : {

*(.i2s_tx)

}

.preinit_array : {

__preinit_array_start = . ;

*(.preinit_array)

__preinit_array_end = . ;

}

...resto del linker script...

Audio de ejemplo

Se ha partido de un sample de dominio público consistente en dos golpes de bombo y caja con charles en medio, típicos del estilo de música house. La muestra se emite en 16 bits con una frecuencia de muestreo de 32050 Hz (Se ha usado este frecuencia por razones de espacio en la memoria flash: es una frecuencia que permite reproducir a una calidad buena manteniendo un tamaño lo suficientemente limitado como para caber en la memoria flash del microcontrolador).

Todo el código fuente puede descargarse de la sección soft.

Lo sentimos. No se permiten nuevos comentarios después de 90 días.

Calendario

Calendario